fft processor chip

In this approach vector and scalar processors are interconnected through shared memory to minimize data. Thereafter FFT starts processing input data.

The objective is to determine the overall structure of the auto placement and routing.

. Download scientific diagram Chip layout of hightech FFT processor. Table 62 is the features of our FFT chip design. The design is based on a decimation-in-frequency radix-2 algorithm and employs in-place computation to opti-mize memory usage.

Calculates 2 to 256 point DFTs on up to 24-bit input data in each I and Q with 24-bit complex outputs. RAM equivalent of 116 x 16 at most a 32-point FFT 16-bit REAL IMAGINARY data can be implemented using on-chip RAM. A high-performance photonic chipset for computing 1-D complex fast Fourier transform FFT calculations.

A 1024-point single-chip FFT processor namedSpiffee was designed and fabricated. These bits are buffered until the remaining bits are available for processing at the input stage. Figure 612 shows a schematic of QFP package for our FFT chip design.

In this chip design to keep the pin count as 88 the input stage of FFT unit receives 16 bit of data in parallel at each positive edge of the clock pulse. Its pin description is given in Table 61. FFTW supports fast transforms of purely real input or output data.

Download Citation Design FFT processor based on FPGA In this paper the design of decimation in time Radix-2 FFT processor is presented which is integrated in FPGA chip regarding FPGA as. FFTW employs O n log n algorithms for all lengths including prime numbers. The processor is then.

The implementation leverages a runtime code generator to support a wide variety of FFT dimensions. Performance depends on a deep understanding of how the OpenCL API maps to the. Real-time Earth observation has become essential for many applications such as natural disasters monitoring coastal maritime surveillance and winter navigation in polar seas.

16-point 24-bit 06um 60MHz 1688mm2 FFT chip by G. A Low-Memory-Access Length-Adaptive Architecture for 2 n n. The PIC17C42 has instructions TABLRD TABLWT to transfer data between program memory space and on-chip file registers.

The full-custom design contains 460000 transistors and was fabricated in a standard single-poly triple-metal CMOS process using 07 m design rules with m. The Fast Fourier transformation FFT is being employed in the algorithms of digital signal processing and in communication systems for several. 44 rows Austek A41102 single chip 256-point complex FFT processor.

In order to operate the processor data must first be loaded into the internal RAM. FFTW supports both one one-dimensional and multi-dimensional transforms. The die size of our FFT chip is.

We sketch a floor plan for the FFT chip depicted in Figure 611. Specifications of the FFT co-processor chip. Salsano Send me a link you know of.

The FFT is a class of efficient DFT implementations that produce results identical to the DFT in far fewer cycles. Download Citation Realization of floating-point FFT processor with FPGA chip The FPGA realization of a floating-point FFT processor is. Here is a list of some of FFTWs more interesting features 9.

Source publication 6 A Spaceborne Synthetic Aperture Radar Partial Fixed-Point Imaging System Using a Field- Programmable Gate. PMOS thresholds are 930 mV and NMOS thresholds are 680 mV. Download scientific diagram Chip microphotograph of the proposed FFT processor from publication.

A VLSI single chip programmable FFT processor suitable for the ESA OSPS able to process 32 64 128 and 256 complex points FFT with an input data rate of 50 Mcomplexsamples is presented. 256-point FFTs calculated in 1024 usec. High Resolution Single-Chip Radix II FFT Processor for High- Tech Application.

Such a product the DSP-449 from PCM Systems combines a Sharp LH9124 block floating-point vector processor with two Texas Instruments TMS320C40 scalar DSP processors to form a VME-based board suitable for high-speed FFT-based DSP applications. The input data can have arbitrary length. Since 64-point FFT unit was considered there was a latency of 4 clock cycles.

The Cooley -Tukey algorithm is a widely used FFT algorithm that exploits a divide- and-conquer approach to recursively decompose the DFT computation into smaller and smaller DFT computations until the simplest computation remains. To compute higher point FFTs the data can be stored in the program memory space of the PIC17C42. The research article focuses on the hardware chip performance analysis of the variable length FFT processor architectures on Field Programmable Gate Array FPGA platform using VHDL programming in.

The Fast Fourier Transform FFT processor is a FFT engine developed for the AT40K family of Field Programmable Gate Arrays FPGAs. The processor occupies 5985. This article discusses techniques to optimize the Fast Fourier Transform FFT for Intel Processor Graphics without using Shared Local Memory SLM or vendor extensions.

Flip-chip integration is used to combine submicron CMOS ICs with GaAs chips containing 2-D.

Fft Processor Architecture A Butterfly Architecture The Most Download Scientific Diagram

High Resolution Single Chip Radix Ii Fft Processor For High Tech Application Intechopen

Pdf Fast Performance Pipeline Re Configurable Fft Processor Based On Radix 22 For Variable Length N Semantic Scholar

Pdf A Low Power High Performance 1024 Point Fft Processor Semantic Scholar

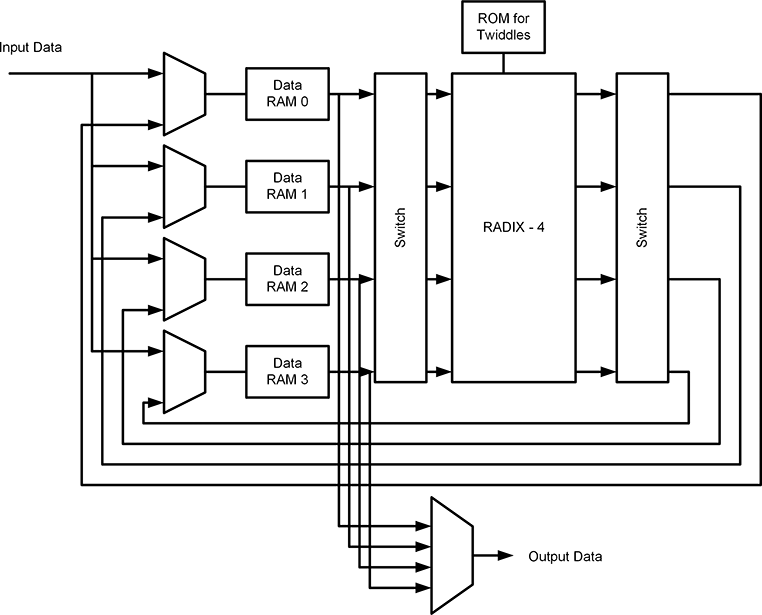

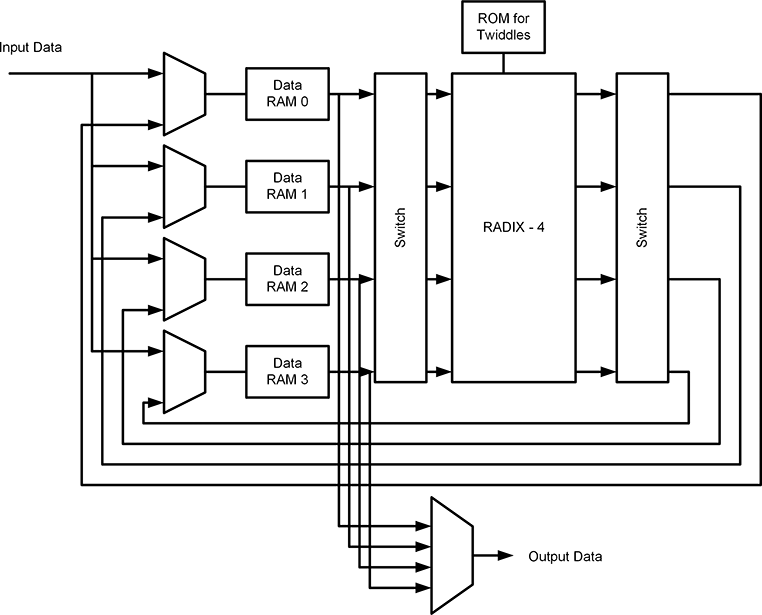

Fft Chip Architecture Download Scientific Diagram

Architecture Of Fft Processor Download Scientific Diagram

A Prototype Analog Mixed Signal Fast Fourier Transform Processor Ic For Ofdm Receivers Semantic Scholar

Pdf Vlsi Design Of Low Cost And High Precision Fixed Point Reconfigurable Fft Processors Semantic Scholar

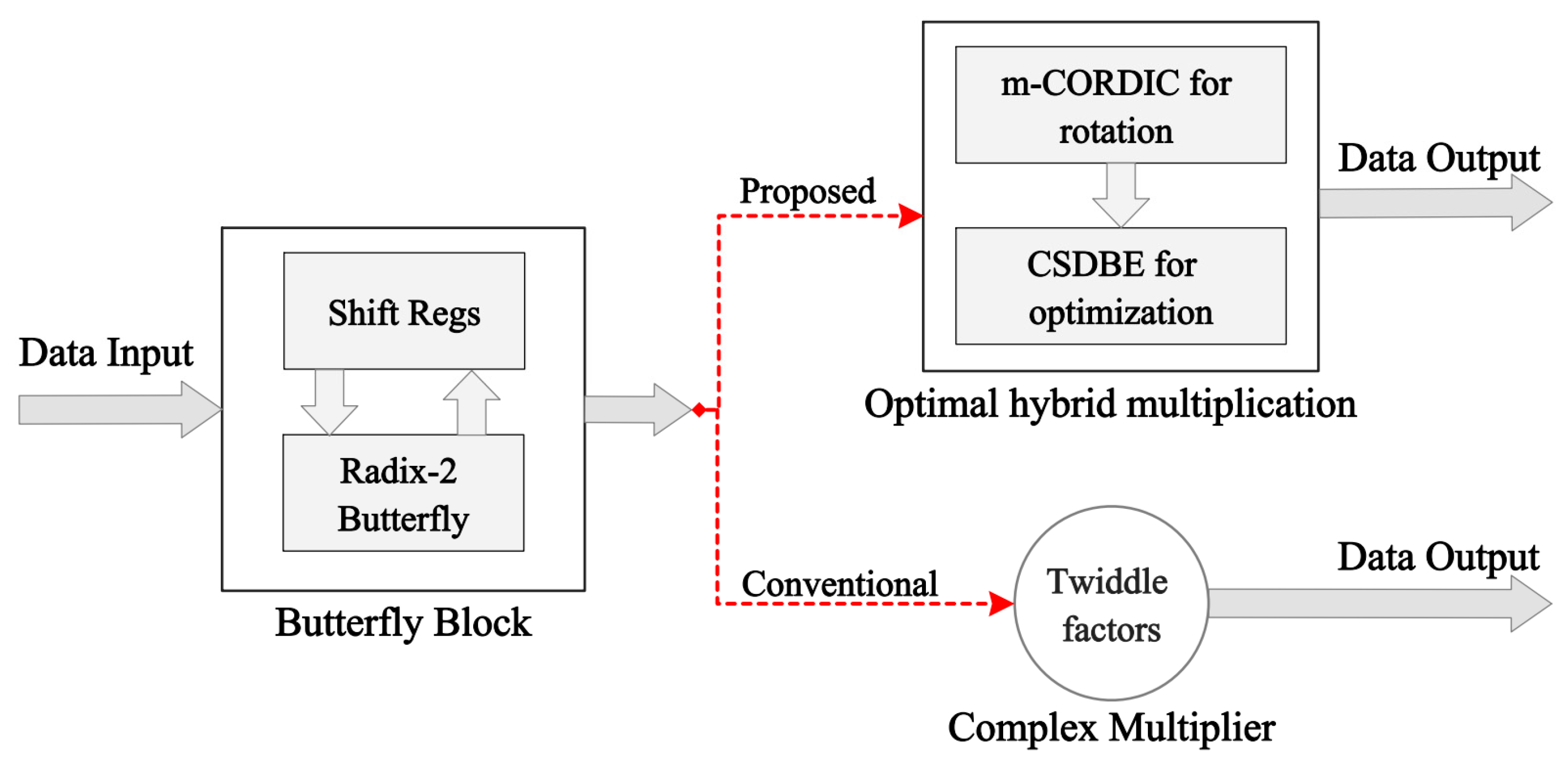

Electronics Free Full Text A Pipelined Fft Processor Using An Optimal Hybrid Rotation Scheme For Complex Multiplication Design Fpga Implementation And Analysis Html

Dft With Fft Algorithm Using Tms320c67xx Dsp Processor Youtube

The Proposed Variable Length Fft Ifft Processor Architecture Download Scientific Diagram

Block Diagram Of Reconfigurable Fft Processor Download Scientific Diagram

Figure 5 From Design Of 16 Point Radix 4 Fast Fourier Transform In 0 18aµm Cmos Technology Semantic Scholar

High Resolution Single Chip Radix Ii Fft Processor For High Tech Application Intechopen

Chip Microphotograph Of The Proposed Fft Processor Download Scientific Diagram

Comments

Post a Comment